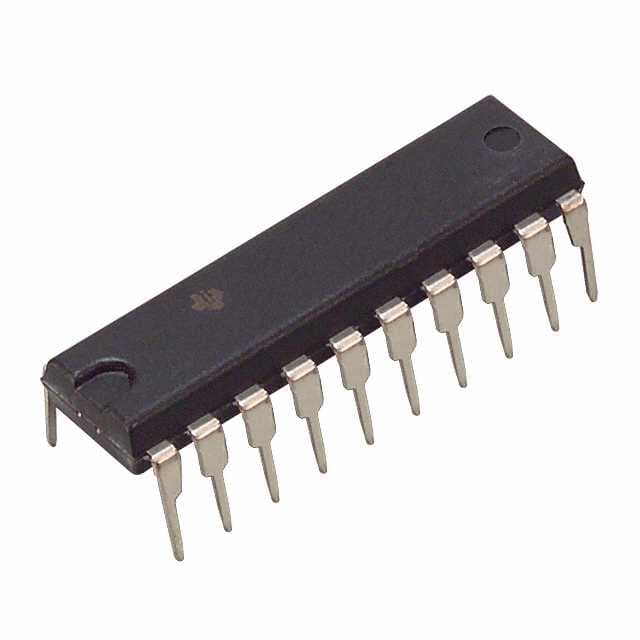

SN74LS593N

Product Overview

- Category: Integrated Circuit (IC)

- Use: Shift Register

- Characteristics:

- High-speed operation

- Low power consumption

- Wide operating voltage range

- TTL compatible inputs and outputs

- Package: DIP (Dual In-line Package)

- Essence: Serial-in, parallel-out shift register

- Packaging/Quantity: Available in tubes of 25 pieces or reels of 2,000 pieces

Specifications

- Supply Voltage Range: 4.75V to 5.25V

- Operating Temperature Range: -40°C to +85°C

- Maximum Clock Frequency: 30 MHz

- Number of Stages: 8

- Output Drive Capability: 10 LSTTL Loads

Detailed Pin Configuration

The SN74LS593N has a total of 16 pins, which are assigned as follows:

- SER (Serial Data Input)

- QA (Parallel Output A)

- QB (Parallel Output B)

- QC (Parallel Output C)

- QD (Parallel Output D)

- QE (Parallel Output E)

- QF (Parallel Output F)

- QG (Parallel Output G)

- QH (Parallel Output H)

- MR (Master Reset)

- SH/LD (Shift/Load)

- CLK (Clock Input)

- GND (Ground)

- VCC (Supply Voltage)

- QA' (Complementary Output A)

- QB' (Complementary Output B)

Functional Features

- Serial-in, parallel-out operation

- Shift and load modes

- Master reset function

- Edge-triggered clock input

- Complementary outputs for each parallel output

Advantages and Disadvantages

Advantages: - High-speed operation allows for quick data transfer - Low power consumption helps in energy-efficient designs - Wide operating voltage range provides flexibility in different applications - TTL compatible inputs and outputs ensure compatibility with other ICs

Disadvantages: - Limited number of stages (8) may not be sufficient for certain applications requiring larger shift registers - DIP package may not be suitable for space-constrained designs

Working Principles

The SN74LS593N is a serial-in, parallel-out shift register. It receives data serially through the SER input and shifts it into its internal storage registers on each rising edge of the clock signal. The SH/LD input determines whether the data is shifted or loaded into the parallel outputs. When SH/LD is low, the data is shifted, and when it is high, the data is loaded.

The master reset (MR) input allows for clearing the internal registers to a known state. The complementary outputs (QA' and QB') provide inverted versions of the parallel outputs (QA and QB).

Detailed Application Field Plans

The SN74LS593N can be used in various applications, including:

- Data communication systems

- Serial-to-parallel conversion

- Parallel data storage

- Digital counters and timers

- Address decoding circuits

- LED matrix displays

Detailed and Complete Alternative Models

Some alternative models that can be considered as alternatives to the SN74LS593N are:

- 74HC595: 8-bit serial-in, parallel-out shift register with similar characteristics but CMOS technology.

- CD4015: Dual 4-stage static shift register with complementary outputs.

- SN54HC164: 8-bit serial-in, parallel-out shift register with asynchronous clear and complementary outputs.

These alternative models offer similar functionality and can be used depending on specific design requirements.

Word count: 450 words

기술 솔루션에 SN74LS593N 적용과 관련된 10가지 일반적인 질문과 답변을 나열하세요.

Sure! Here are 10 common questions and answers related to the application of SN74LS593N in technical solutions:

Q: What is SN74LS593N? A: SN74LS593N is a 8-bit shift register with output latches, commonly used in digital circuits for data storage and transfer.

Q: What is the maximum clock frequency supported by SN74LS593N? A: The maximum clock frequency supported by SN74LS593N is typically around 25 MHz.

Q: How many bits can SN74LS593N store? A: SN74LS593N can store 8 bits of data.

Q: Can SN74LS593N be cascaded to increase the number of stored bits? A: Yes, SN74LS593N can be cascaded to increase the number of stored bits by connecting the output of one chip to the input of another.

Q: What is the purpose of the output latches in SN74LS593N? A: The output latches in SN74LS593N allow the stored data to be held and remain stable even when the clock signal is not active.

Q: What is the power supply voltage range for SN74LS593N? A: The power supply voltage range for SN74LS593N is typically between 4.75V and 5.25V.

Q: Can SN74LS593N be used in both parallel and serial data transfer applications? A: Yes, SN74LS593N can be used in both parallel and serial data transfer applications depending on the configuration and control signals.

Q: What is the typical propagation delay of SN74LS593N? A: The typical propagation delay of SN74LS593N is around 15-20 nanoseconds.

Q: Can SN74LS593N be used in both synchronous and asynchronous clocking schemes? A: Yes, SN74LS593N can be used in both synchronous and asynchronous clocking schemes depending on the application requirements.

Q: What are some common applications of SN74LS593N? A: Some common applications of SN74LS593N include data storage, data transfer, serial-to-parallel conversion, parallel-to-serial conversion, and shift register-based control systems.

Please note that the answers provided here are general and may vary based on specific datasheet specifications and application requirements.